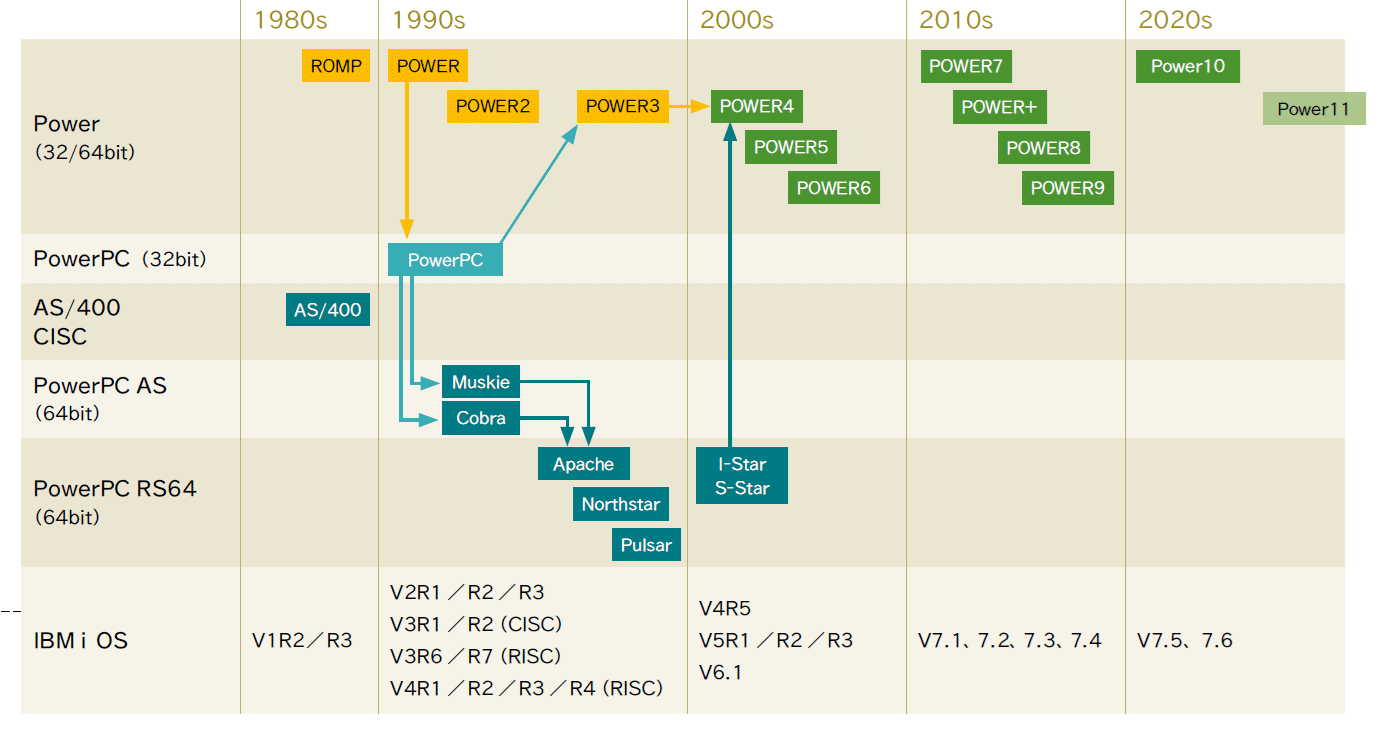

「テクノロジーではなくビジネスを考える」ためのシステムであるIBM iでは、x86/x64系とは異なり、プロセッサそのものへの言及というのは伝統的に重視されてこなかったと思われる(AS/400のCPUの詳細なんて、誰が気にしただろうか)。

それはIBM iのコンセプトの成功を意味してはいる。それでもpSeriesとの統合後は、当然プロセッサの紹介は増えたものの、「7、8、9、10…番号が順調に増えているな」くらいの受け取り方が多いかもしれない。そこで、ここではIBM iを支えてきた個性的なPowerプロセッサたちを少し紹介できればと思う。

ただし筆者も(読者と同様に)IBM iに携わる一介のSEであり、専門知識はどうしても限られる。そこで可能な限り参考資料を挙げたので、関心のある人はぜひそちらを参照されたい(注1)。

IBMはチップ単体ではなくサーバーを作る会社であり、IBM Powerもその観点で捉える必要があるはずだ。現在ではサーバーと言えど、PCと共通のテクノロジーに立脚しているが、大量の仕事をこなすことに特化しているのが特徴である(参考資料*1)。

よってプロセッサの能力だけでなく入出力性能、拡張性、信頼性、電力消費量など、地味ではあるが重視されるいろいろな要素がある(図表1)。

POWERからPOWER3、およびPowerPC

Power ISA(Instruction Set Architecture)を持つ最初のプロセッサであるPOWERは、IBM RS/6000(1990年に発売)に搭載されて発売された。これは32bitのRISCで、最大の特徴はスーパースケーラー(実行ユニットを複数搭載し複数命令を同時に実行できる能力)であった。

次のPOWER2(1993年に発売)は、いわゆるスーパーコンピュータのイメージの1つになった特徴的な外観を持つMPP(Massive Parallel Processor)であるRS/6000 SP(Scalable POWER

parallel)に搭載された。有名なスパコンである「Deep Blue」は、このSPを元に開発された。

POWER3(1998年に発売)は、32bit系のPowerPCと合流する形で64bit化された。スパコン「ASCII White」は、POWER3を搭載したRS/6000を元に開発された。これらはいずれも科学技術計算を主な用途としており、性能向上のために何らかの形での並列性を追求していたと捉えられる。

一方で、POWERから派生する形でApple-IBM-MotorolaのアライアンスによるPowerPCが生まれた。これは32bitで、最も有名な搭載機はAppleのPower Macintosh系列であろう。それ以外にゲーム機や、制約の大きい環境下でも高性能が必要な航空宇宙分野で数多く採用された(注2、注3)。

この系列を搭載したスパコンとしては、有名な「Blue Gene」や「Roadrunner」がある。

PowerPC ASおよびPowerPC RS64

この開発過程は、(参考資料*6、7)に詳しいので簡単にとどめたい。RISC技術の有効性は明らかになったが、ビジネス用途のAS/400に既存のPowerPCでは不足と判断された。

理由はいろいろあるが、主に計算能力それ自体よりも、システムとして大量のデータを効率よく扱う能力が重要だからという結論だった。これを補うためにPowerPCのISAを拡張し、その上にAS/400のMIを移植・稼働できるようにしたのがPowerPC ASである。

これは数世代に渡り拡張され、記憶共用型マルチプロセッサ(SMP:Shared Memory ProcessorまたはSymmetric MultiProcessor)の大型機が登場した。さらにRS64として発展し、RS/6000のビジネス用途向け大型機と共有されるに至った。

この系列のマシンは有名なスパコンには(当然)使われていないが、メモリやI/Oの構造には、大量データを処理するサーバーに向けた各種の工夫が凝らされている。プロセッサだけが早くても、データの供給が追いつかなければ、その能力はまったくの無駄になってしまうからだ(注4)。

POWER4以降

POWER4(2001年に発売)は、IBMの歴史の中でもエポックメイキングなプロセッサとして記憶されるだろう。コードネーム「Gigaprocessor」として初めて動作周波数1GHzを超えるとともに、その搭載機「Regatta」は、その後のPower Systems系列のサーバーの基礎となった。IBM iの観点からも、ついにハードウェアの統合がなされた意味は非常に大きい(参考資料*8)。

POWER4は単にマルチコアの高速プロセッサというだけではなく、あくまでサーバー用に最適化して設計されているのが特徴だ。Regattaは全体としてNUMA(Non Uniform Memory Access)と呼ばれるデザインを採用し、これによりOSやアプリケーションに非互換性をもたらすことなくSMPを超える拡張性を得ている。

システムが階層的に構成されており、CPUを増やすとそれに応じてメモリやI/Oもバランスよく増やせて、ボトルネックを作らないようになっている。他のシステムよりも少ないCPUで同等以上の負荷をさばける効率性、Dynamic LPARや信頼性向上もサーバー用途にとって重要であった。

続いてPOWER5(2004年に発売)は、製造技術を高めてSMT(Simultaneous Multi Threading)を導入し、1つのコアで2つのスレッドを処理できた。

POWER6(2007年に発売)は、パイプライン段数を増やして動作周波数を上げ、5GHzに達した。

POWER7(2010年に発売)は動作周波数を抑えたが、チップあたりのコア数が8になり、SMTのスレッド数も増加した。クイズ番組で人間のチャンピオンを破ったことで有名なシステム「Watson」はPOWER7を用いていた。

POWER8(2014年に発売)では、さらにマルチコア・マルチスレッド化が進んだ。またCPUに代わって特定の処理だけを担当する各種ハードウェア機構が増やされた。

またCAPI(Coherent Accelerator Processor Interface)が搭載されたが、これはPOWER9でのスパコン実現の布石だった。

2000年代中盤になると、いわゆる「電力の壁」(参考資料*1)により、周波数向上でコアの性能を単純に上げていくことが難しくなり、トランジスタの微細化によって生まれたスペースに数多くのコアやキャッシュメモリ、さらに専門分化した各種ユニットを詰め込むことで、システム全体のスループットを増やす方向に進んだ。

これは単一ジョブのパフォーマンス向上には必ずしもつながらないが、並列処理でサーバー全体としてのキャパシティを増やすことにつながった。

POWER9およびPower10

現在Power ISAを管理しているのはOpenPOWER Foundation で、一部の機能以外は情報が公開されている。POWER9からはPower ISAがバージョン3になった(注5)。

POWER9(2017年に発売)では、さらにマルチコア化が進んだ。またスケールアウト用(SO)とスケールアップ用(SU)が分化し、用途に応じた構成が取れるようになった。

有名なスパコン「Summit」と「Sierra」は、POWER9 CPUとNVIDIAのGPUを組み合わせたヘテロジニアスなデザインで、CPUとGPU間はCAPIから進化した高速リンクで接続、またノード間はInfinibandで同じく高速接続している。

この構成は、POWER9システム全体のデータ転送能力が極めて高いことにより可能になっている。Power10(2021年に発売)では、新しいインターフェースとしてOMI(Open Memory Interface)と、大規模な共有メモリクラスターを実現する基礎となるPowerAXONが追加された。

これらも、何らかの今後の布石であると思われる。ほかにも電力効率やセキュリティの改善、追加のGPUなしでもAIワークロードを処理できるMMX(Matrix-Multiply Assist)搭載などがある。

POWER4から9にかけての変遷に関して一覧性のあるものとしては、(参考資料*11)が読みやすい。POWER/PowerPCアーキテクチャのスパコンたちについては、日本IBMのサイトにコンパクトにまとまっていた。(参考資料*12)やWikipediaも手軽に参照できる情報源であった。

これまでのところ、新型のPowerプロセッサの詳細は学会や業界のシンポジウムでIBMから説明されてきた。執筆時点ではPower11の詳細は未発表だが、2025年にはそれが搭載されたサーバーの発表が予想されている。それがIBM i の世界に何をもたらすか、期待して待ちたい。

[注1]ここでは参考資料*1~5を紹介する。参考資料*1は少々ハードルが高いが、参考資料*2はより手軽で入手も容易。参考資料*3~5の著者のHisa Ando氏は近年引退したようで残念だが、Webに数多くの記事が書かれており、いずれもまだ参照可能である。

[注2]この系列にも64bitプロセッサはある(AppleのG5やCell BE)が、直接IBM iへとつながるものではないので、ここでは省略した。

[注3]PlayStation3に搭載されたCell BE(Broadband Engine)は、現在主流となっているGPU搭載機のデザインを先取りしたアーキテクチャだった(参考資料*4)。

[注4]参考資料*1には、記憶階層の説明に以下のような例えがある。

L1キャッシュ:台所の冷蔵庫

L2キャッシュ:家の中の冷凍冷蔵庫

L3キャッシュ:家のガレージまたは地下室の冷凍冷蔵庫

主記憶:食料品店の業務用冷凍冷蔵庫

2次記憶:食料品店の業務用冷凍冷蔵庫へ納品する食品業者

ここでの説明はないが、CPUのレジスタはおそらくまな板の上ということになるだろう。また冷凍とは、解凍する時間が必要という意味。キャッシュミスがいかに性能に響くか、直感以上のものがある。CPUをデータ待ちで遊ばせないためには、あらゆる創意工夫が必要になるはずだ。

[注5]OpenPOWER Foundationは参考資料*9にURLを記した。2025年1月時点でISAドキュメントのバージョンは3.1cで、Book I、Ⅱ、Ⅲの3部構成は変わっていない。なおここから到達可能なリソースとして、International Conference on Supercomputing 2020のワークショップ資料がある。ISAの変遷や互換性基準についての説明資料。なおIBM i用のタグアクティブモードに関わる機能は、これまでも公開されたことはなかったとは言え、ここで標準機能ではなく「sandbox」とよばれる実装依存のカテゴリに分類された模様(参考資料*10)。

【参考資料】

*1: 『コンピュータの構成と設計 第6版(上下巻)』(D.パターソン・J.ヘネシー著/成田光彰訳、日経BP、2021)

*2: 『特集1 一度は学んでおきたいCPUの仕組み』(Software Design 2023年4月号、技術評論社)

*3: 『高性能コンピュータ技術の基礎』(Hisa Ando著、毎日コミュニケーションズ、2011)

*4: 『プロセッサを支える技術 果てしなくスピードを追求する世界』(Hisa Ando著、技術評論社、2011)

*5: 『GPUを支える技術 超並列ハードウェアの快進撃[技術基礎]』第2版(Hisa Ando著、技術評論社、2021)

*6: 『Inside the AS/400 日本語版』(F.G.ソルティス著/日本アイ・ビー・エム訳、インフォ・クリエイツ、1998)

*7: 『Fortress Rochester:the inside story of the IBM iSeries』(F.G.ソルティス著、29th Street Press、2000)

*8: 『IBM Heritage history The IBM Power4』(https://www.ibm.com/history/power、2025年1月時点)

*9: OpenPOWER Foundation(https://openpower.foundation.org/、2025年1月時点)

*10: 『The Open Power ISA: Architecture Compliancy and Future Foundations』(Brian Thompto、Workshop on RISC-V and OpenPOWER, International Conference on Supercomputing, 2020)(https://ics2020.bsc.es/sites/default/files/uploaded/brian_thompto_ICS2020_SLIDES.pdf、2025年1月時点)

*11: 『業界に多大な影響を与えた現存メーカー サーバー事業が現役のIBM』(https://ascii.jp/elem/000/001/

833/1833200/、2025年1月時点)

*12: 『これまでも、これからも、スパコンの技術革新に貢献する』(IBM Power Systems、IBM Systems Japan blog)(https://www.ibm.com/blogs/systems/jp-ja/until-now-and-future-power-systems-contributes-to-supercomputer-technology-innovation/、2025年1月時点)

著者

伊藤信明氏

リコージャパン株式会社

デジタルサービス企画本部

PP事業部 SI技術室

基幹システムグループ

情報システム学修士(専門職)

文系四大卒で、新卒日本IBM入社です。2000年代に社会人大学院を修了し(IBM出身の実務系の先生も2人いました)、だいぶ視野が広がったので、もしそういうことに少しでも関心を持つ読者がいてくれればということと、あとは「リコーの人がこれを書いてるけど内容信じていいの?」という至極もっともな疑問に対して多少箔をつけるというのが、本稿執筆の意図です。

[i Magazine 2025 Summer号掲載]