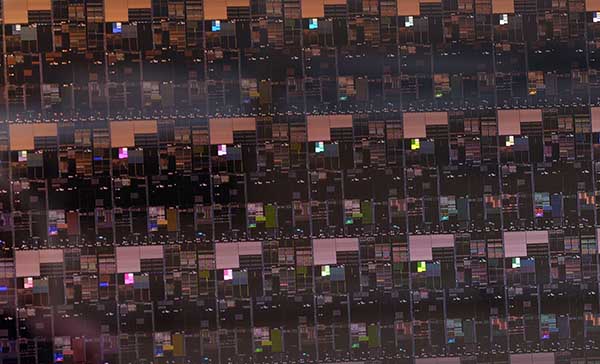

IBMは5月6日(現地時間)、線幅2ナノメートル(nm)のNanosheet(ナノシート)技術を採用した半導体チップを開発した、と発表した。線幅2nmの半導体チップは「世界初」(IBM)。指の爪ほどの大きさのチップに500億個のトランジスタを搭載するという(2017年発表の5nmチップは約300億トランジスタ)。量産開始の目標時期は、2024年後半。

性能を、今年発売される予定のPower Systems搭載の7nmチップ(POWER10プロセッサ)と比較すると、電力量で45%の性能向上、エネルギー消費で75%の削減が見込まれている。また、このチップの利用により、携帯電話のバッテリー寿命を4倍に、言語翻訳をより簡単に、自律走行車(自動運転車)の物体検知や反応速度を高速化し、データセンターの二酸化炭素排出量を大幅に削減するなどのメリットがある。IBMの試算では、世界のすべてのデータセンターが2nmベースのプロセッサにサーバーを変更した場合、4300万世帯分の電力を節約できるという。

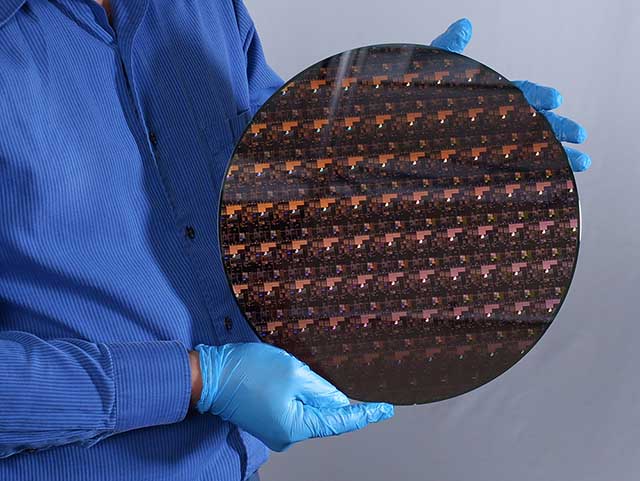

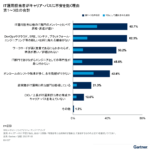

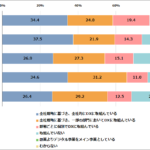

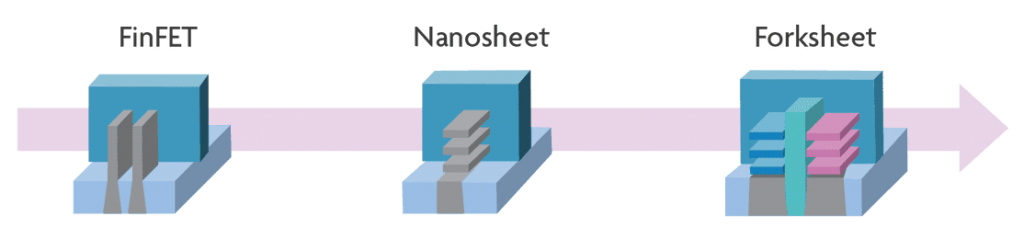

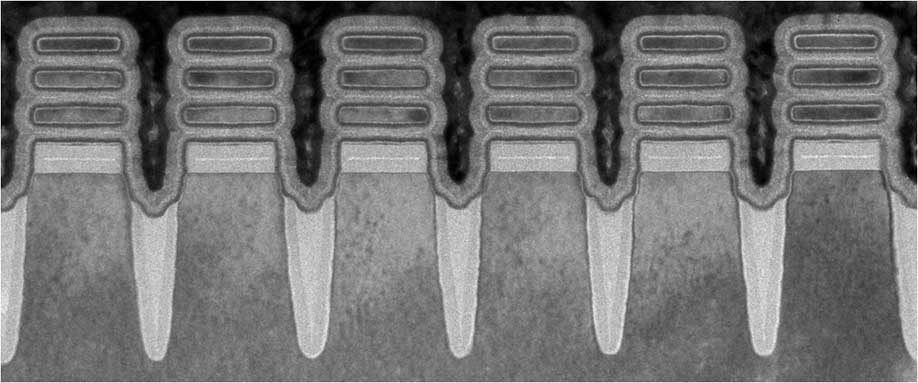

今回の2nmチップは、30センチのバルクウエハー(上写真の円盤)上にNanosheet技術で製造されている。Nanosheet技術は、ウエハー上に薄いシートを重ねるような技術で(今回は3層)、従来からのFinFET技術に代わる技術として期待されている(下図表)。

ただし、世界最大の半導体ファンダリ企業である台湾のTSMC(aiwan Semiconductor Manufacturing Company)は次世代の3nmチップをFinFET技術ベースで製造することを表明しており、米国の半導体メディアの間では、今回の2nmチップの発表を「TSMCとIBM連合の一騎打ち」とする見方もある。

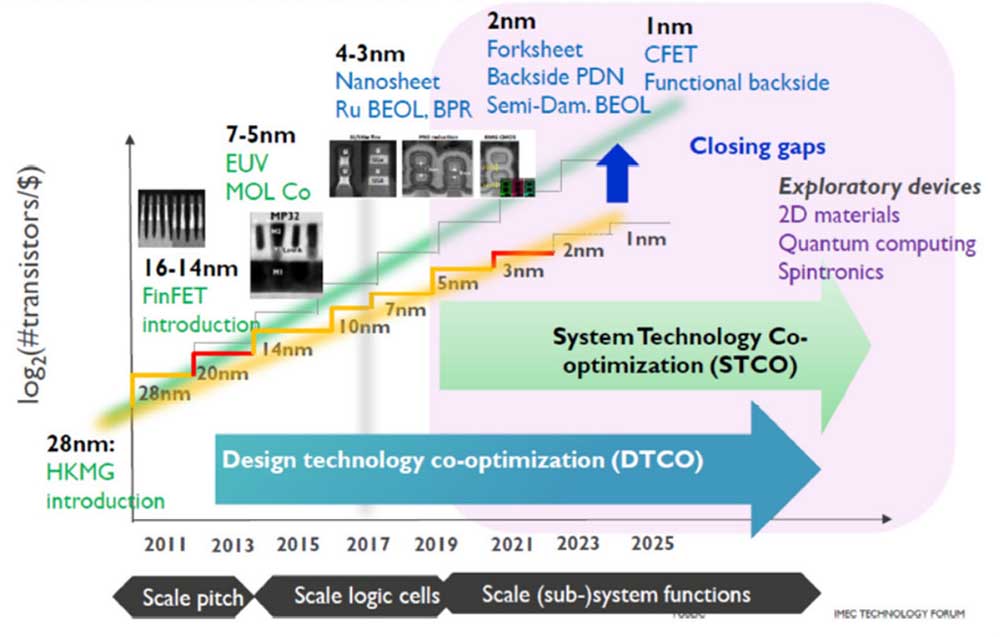

世界の半導体市場では、今なお激しい開発競争が続いている。TSMCは5nmチップ搭載のM1とA14プロセッサをアップル向けに製造し(2020年秋)、韓国のサムスン電子も5nmベースのSnapdragon888をQualcomm向けに提供済みである。半導体チップは、さまざまな技術要素により性能が決まるので回路線幅だけで見ることはできないが、回路を細線化して集積度を上げる競争は継続している。実際、TSMCは2022年に4nmと3nmの量産化を開始する予定であり、ベルギーの非営利研究・開発機関imec(Interuniversity Microelectronics Centre)は1nmチップへのロードマップを示している。

今回の2nmチップの量産開始は2024年目標とされているが、今年登場するPOWER10の次のPOWER11も2024年のリリースが予想される(POWERプロセッサの更新は3年周期)。7nm(POWER10)から2nmへ一挙に飛躍するのか、それとも5nmベースを経由して、その次のPOWER12になるのか、IBMは公表していない。

◎参考

imecブログ「Scaling CMOS beyond FinFETs: from nanosheets and forksheets to CFETs」

[i Magazine・IS magazine]